Full Library / Hardware_Modeling / Utility / Register_Expr_N

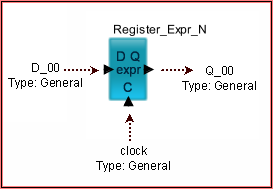

Block Name: Register_Expr_N

Code File Location: VisualSim/actor/lib/fpga/Register_Expr_N

A polymorphic register, which routes input tokens to a matching output port, with the same _nn desination in the port name. The defaults are D_00, Q_00. This actor supports multiple input ports, the D_00 port for incoming data tokens, and the clock port to trigger the corresponding output data path, assuming an input value exists. When the clock port fires, a clock token is available at the clock input, and at least one input port token is available on the D_NN port, then that token is read, and sent to the corresponding output port based on the port naming, Q_NN. Input ports can be over-written, waiting for the next clock to arrive, either clock port, virtual reference, or a speed Mhz. The speed Mhz option generates it's own internal clock to the block, once a simulation starts, no action by the user is required. The data entered into a register can be any Token supported by VisualSim, such as integer, long, double, boolean, string, array, or record. The user just needs to set the appropriate port type in some cases.

User can add ports, as long as naming convention is maintained for passing values from D_NN input to corresponding Q_NN output port. In addition, one can utilize expressions from the reading of input tokens till a clock arrives. If the Expression_NN is set to none, then input port will be passed to the output port. Note: currently one cannot guarantee the order of Expression_NN execution, as it is dependent on a hash map.

Refer Register_Expr_N Demo Model.

Parameter |

Explanation |

Type |

Example |

Clock_Type |

The type of Register clocking. This is a string-valued attribute that defaults to "AND", meaning all input ports must be available to fire the Regsiter. "OR" means any input to the Register will send out a Response to that port. If another port had not yet received any value the first time, then no output. Ports that have previously received at least one input will output their persistence value. |

- |

AND |

Clock_Source |

Default is trigger the clock input externally, alternatively provide a virtual name reference, or enter a speed in Mhz for self-clocking (double value such as 10.0). |

String |

clockPort_or_virtualRef_or_speedMhz |

Expression_00 |

RegEx expression, can include Result = Expression, see DS_Expression block for more details. |

String |

MyRegExpression_00_or_None |

Port |

Explanation |

D_00 |

Input port for data tokens. |

Q_00 |

Output port, type same as input. |

clock |

Input port for clock tokens. The type is any type. |

Created with the Personal Edition of HelpNDoc: Easily create PDF Help documents