Interfaces and

Buses/Networking/ETH_Switch/EtherSwitch

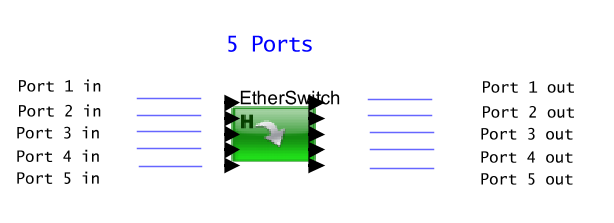

Block Name: EtherSwitch

Code

File Location: VisualSim/actor/arch/ETH_Switch/EtherSwitch

Description

The Ethernet

Semiconductor Library provides the user with a configurable EtherSwitch

that emulates the accurate functionality, timing, and power behavior of

the semiconductor device. This library block is based on the datasheet

of a variety semiconductor products especially, the NXP Semiconductor

N.V. product SJA1105TEL (https://www.nxp.com/part/SJA1105TEL#/). The

library block can be used to evaluate the performance of a

semiconductor device in the network architecture or to optimize the

Ethernet Switch internal architecture or compare the Ethernet Switch

from different vendors.

The default

library is a 5 port Ethernet Switch that can be scaled to add more

ports and emulate data center devices. The library component supports

MII interface, PHY, transmitter/receiver queue, shared frame buffers,

processor cores, policies, forward and scheduling. The Ethernet Switch

library block can be integrated with other VisualSim standard protocol

components (CAN, LIN, Wireless, PCIe and VPX) through the Gateway

library to create a full Automotive, Integrated Avionics Modular System

or Data Center network model. The hardware, software and shared

resources have been parameterized for easy configuring to create a

specific implementation. The underlying code for the Ethernet Switch

block is provided as part of this library.

This library

helps the user find answer to:

Select the right semiconductor

device for the target newtwork to meet the timing requirements

|

Hardware-software

partitioning, frame buffer sizing and memory allocation for all the

tables of proprietary Ethernet Switch to guarantee real time responses.

|

Optimize

the traffic shapping and scheduling algorithms to ensure maximum

throughput and no interference on timing triggered packets.

|

Identify system bottlenecks in the network and in the device hardware

|

Memory allocation for Ingress and Egress buffering

|

Number of Processor Cores

|

Measure the power consumption based on the selected device and configuration.

|

Impact of failures on response time and throughput

|

Standard

|

Description

|

IEEE

802.1Qbv

|

Time

Aware Shaping

|

IEEE

802.1Qbu & IEEE 802.3br

|

Preemption

|

IEEE

802.1Qca

|

Path

control and Reservation

|

IEEE

802.1Qcc

|

Stream

Reservation Protocol

|

IEEE

802.1Qci

|

Per

Stream Filtering and Policing

|

IEEE

802.1Qcb

|

Frame

Replication and elimination

|

IEEE

802.1Qch

|

Cyclic

Frequency and Forwarding

|

IEEE

802.1As

|

Enhanced

Generic Precision Time Protocol

|

Refer EtherSwitch

Demo Model.

Click here to watch the description video on EtherSwitch:

https://youtu.be/mPblaqbWOtw

Ingress Stage

A frame is received from a neighboring PHY or MAC

on one of the available ports. The xMII block passes received data to

the Receive MAC (RX MAC) connected to the reception port. The RX MAC

performs low-level checks on the frame data and reports any CRC or MII

errors detected to the status and control unit. The frame is

immediately discarded when a low-level error is detected. A frame that

passes all low-level checks is stored in frame memory in 128 byte

segments. The RX MAC captures an ingress timestamp, extracts meta

information from the frame and forwards it to the Input Queue (IQ). If

a VLAN tag was not embedded in the received frame, the RX MAC block

assigns a configured Port VLAN ID and a configured Port VLAN Priority

to the frame. The IQ module stores the frame meta information in a

deterministic order and passes it to the forwarding stage for further

processing. If multiple frames are received at the same time on

different ports, the processing order is determined by the port

numbers; a frame received on a port with a lower ID is processed before

a frame received on a port with a higher ID. Note that this only

influences the frame order on the egress stage if multiple concurrently

received frames are forwarded to the same destination port.

Forwarding Stage

Once a valid MAC-level frame has been forwarded by the ingress stage,

the forwarding stage applies several higher-layer checks on the frame

and extracts the forwarding information.

The VLAN Lookup (VLAN_LU) block reads the VLAN information configured

for the VLAN ID associated with the frame. If a VLAN tag is embedded in

the frame, the block checks if the reception port is configured to be a

member of this VLAN. If it is not, the frame is dropped and reported to

the status and control unit. It also checks if the VLAN associated with

the frame is configured for mirroring or retagging and determines which

egress port it should be transferred to.

The Address Lookup (L2ADDR_LU) block extracts forwarding information

from the source MAC address and VLAN ID to be used with future frames

addressed to this MAC address and VLAN ID combination. The VLAN ID is

ignored during this process if shared address learning is activated.

This block also looks up the destination MAC address and combines it

with the VLAN ID to determine the forwarding information for the frame.

The Policing (L2_POLICE) block meters the incoming frame rate. The

switch can be configured to drop packets if the maximum frame rate is

exceeded.

The Forwarding (L2_FORW) block uses the information obtained from the

other blocks to determine the set of ports to which the frame is

forwarded. The switch can be configured to limit the number of egress

ports accessible to frames received on a specific ingress port. For

example, it is possible to direct that any frame received on a

particular ingress port is only forwarded to a specific egress port,

regardless of the forwarding information provided.

This block also determines the VLAN priority to be embedded in frames

forwarded by the switch as well as the egress priority queue in which a

frame is stored on a per priority and per port basis. It also

determines if the mirroring port shall be included in the set of ports

to which the frame is forwarded, based on the information configured

for port-based and VLAN-based ingress and egress mirroring. The L2_FORW

block also reserves the required memory space in the partition assigned

to the frame by the policing module.

Egress Stage

The egress stage recomposes the frame from the data stored in the frame

memory and the information gathered by the forwarding stage. The

Transmit MAC (TX MAC) assigns the frame to the priority queue

determined by the forwarding stage. It monitors the number of frames

stored in the priority

queue. If the maximum number allowed has been exceeded, the frame is

dropped and an error condition is signaled to the status and control

unit. The TX MAC also performs priority selection based on the

strict-priority algorithm and considers whether the credit-based shaper

assigned to the priority queue is in the transmission-allowed state.

Parameters and Configurations

The EtherSwitch module has the following set of parameters and table configurations:

Parameter

|

Value

|

Description

|

Switch_Name

|

"SW1"

|

Provide

the EtherSwitch name. It has to be a unique value in case you have more than one EtherSwitch Module in the same model.

|

Num_Of_Ports

|

5

|

Provide

the Number of Ports defined for this EtherSwitch. If the user wasnts to

increase the number of ports, then open the EtherSwitch Module and

inistaniate another Port layer similar to the way others are

instantiated.

|

CPU_Clock_Rate_Mhz

|

1000.0

|

Provide the EtherSwitch Speed in Mhz.

|

VLLUPFORMAT

|

0

|

If

value selected is 1, then Stream Identiffication is done Using

VL_ID field. Otherwise Destination MAC and VLAN Tags are used.

|

MIRR_PORT

|

0

|

If mirroring is enabled, then data will be available on this port for Packet analysis.

|

Enable_Mirroring

|

false

|

Set it to true foe enabling this feature

|

Use_TSN_Scheduler

|

false

|

Set it to true for using schedule tables entried for making a decision on when to open and close gates for each of the port.

|

Enable_Debug

|

false

|

Debug

Messages wont be displayed. When set to true, a new window will pop up

and that will display the tracking of every packet entering the

EtherSwitch.

|

Table Configurations:

Schedule Table

This table establishes the link between the synchronization

algorithm and the schedule. If the user does not enable the

Enable_TSN_Scheduler parameter, the schedule will not be active

(whether or not the user loads the Schedule table). The entries

included in an entry point must be sorted in ascending order (i.e.

those having smaller values must be loaded before those with larger

values) according to their respective DELTA values.

PORT

|

Priority

|

DELTA

|

0

|

0

|

1

|

0

|

1

|

5000

|

PORT column defines the port number of that particular entry. Each

Port can have an entry for each priority level. Prioirty values range

from 0 to 7. DELTA column defines the delay before this entry fires in

multiples of 200 ns.

Port VLAN Config Table

This table is used to define the VLAN IN and VLAN Priority for packets which comes in without having those fields in it.

PORT

|

CONF_VLANID

|

CONF_VLANPRIO

|

0

|

1

|

0

|

1

|

10

|

0

|

2

|

2

|

0

|

3

|

40

|

1

|

4

|

7

|

4

|

PORT column defines the Port num. CONF_VLANID column provides

matching VLAN ID for each port. CONF_VLANPRIO column provides matching

VLAN Priority for each port.Max value of VLAN ID = 4096 and Priority

values range between 0 to 7..

xMII Mode Parameters Table

This block is used to set the

xMII mode of operation. When PHY mode is selected, the port on this

switch interface behaves as a PHY and the partner should behave as a

MAC. When MAC mode is selected, the switch interface port behaves as a

MAC and the partner should be a PHY.

PHY_MAC

|

xMII_MODE

|

{0,0,0,0,0}

|

{"b10","b10","b10","b10","b10"}

|

PHY_MAC(PORT) = 1 -> PHY mode

= 0 -> MAC mode

xMII_MODE(PORT) = 00 -> MII

= 01 -> RMII

= 10 -> RGMII

= 11 -> not used

VLAN LU table

This table is used to statically configure VLAN

information. A table entry defines the ports that are members of a

specific VLAN.

Port_Num

|

VLAN_ID

|

VLAN_Priority

|

{3}

|

1

|

0

|

{0,1,4}

|

40

|

1

|

Port_Num column accepts array values. Defines the set of ports on

which a frame tagged with the respective VLAN ID may be received.

L2 POLICING Table

This table defines traffic policing rules for each port

individually, along with a priority value for each port and switch

broadcast traffic. The table has 45 entries. Ethernet frames received

on mappings for which the user has not provided an entry are

automatically mapped to entry 0 (all such traffic is dropped). The

entry to which an incoming frame maps is determined in the following

way: if the incoming frame is classified as broadcast, the matching

entry is 40 + PORT (where PORT is the physical port number between 0

and 4); if the frame is not classified as broadcast, the matching entry

is 8 * PORT + VLANPRIO where VLANPRIO is the VLAN priority value

associated with the frame.

INDEX

|

SMAX

|

RATE

|

MAXLEN

|

PARTITION

|

0

|

1522

|

64000

|

2043

|

1024*1024

|

1

|

1522

|

64000

|

2043

|

1024*1024

|

The algorithm used for bandwidth budgeting works as follows. Each

policing block contains the parameters SMAX and RATE. Initially, the

bandwidth credit of an entry gets

set to SMAX. When a valid Ethernet frame mapping to this entry is

received, the value of the bandwidth credit is decreased by the number

of bytes in the frame (including Ethernet

header and checksum). At times when no traffic associated with this

entry is received, the bandwidth credit gets increased by the value of

RATE every 8 s, to a maximum of SMAX.

An associated frame gets dropped if the resulting value of the

bandwidth credit is less than or equal to zero. This makes it possible

to control the traffic rate individually for each

port. In addition to the rate, each entry specifies the maximum length

of frames associated with this entry and the memory partition that gets

credited for this frame. This makes it

possible to partition the maximum amount of frame memory available for different traffic classes*.

L2 Address Table

The following is the layout of an entry in the L2 Address Lookup table:

MACADDR

|

DESTPORTS

|

VLAN_ID

| ENFPORT

|

INDEX

|

"a1:b2:c3:d4:e5:f6"

|

{2,3}

|

1

| false

|

"hash"

|

MAC Address and VLAN_ID are used to obtain the destination ports to which this packet will be forwarded to.

L2 Forwarding Table

This

table defines the mapping of ingress VLAN priority values to egress

VLAN priority values as well as the mapping of egress VLAN priority

values to priority queues physically available on the transmission

ports. In addition, this table is used to define forwarding limitations

for each ingress port. The first five entries in the table are used for

a per-port based remapping of the ingress priority values to egress

priority values. For instance, the value of VLAN_PMAP in entry 0

defines the mapping of either a received or per-port assigned ingress

priority value pi to an egress priority value po for frames received on

port 0 by assigning po = VLAN_PMAP[pi]. This means that po will be used

as the PCP (Priority Code Point) value on all egress ports forwarding

the frame with a VLAN tag included.

The last eight entries in the table are used for a per-egress

priority-based mapping of logical priority values to physical priority

queues of the different ports. For the previously

obtained egress priority value po, the resulting mapping to priority

queues on each port i is obtained by assigning qi = VLAN_PMAP[i], where

qi is the priority queue used for po on

port i. For example, to map priority value po = 4 to priority queue 1

on port 0 and to priority queue 2 on port 3, the value of VLAN_PMAP for

entry 5 + 4 = 9 must be set to 1 for

index 0 and to 2 for index 3.

BC_DOMAIN

|

REACH_DOMAIN

|

FL_DOMAIN

| VLAN_PMAP

|

{"F","F","F","F","F"}

|

{"T","T","T","T","T"}

|

{"F","F","F","F","T"}

| {1,2,3,4,5,6,7,0}

|

The Domain specifies whether the packet can be forwarded to that particular port. BC stands for Broad Cast.

When a non-BC packet comes in, we check all destinations with Reach

domain and all those ports configured to accept them are passed and

others are dropped.

FL Domain is used to forward an unknown packet received.

VL Lookup Table

The table

establishes the link between the stream identifier and the entry of the

VL Policing table. The identification depends on the setting of the

VLLUPFORMAT flag.

INDEX

|

DESTPORTS

|

ISCRITICAL

| MACADDR

|

VLANID

| PORT

|

VLANPRIOR

|

VLLD

|

0

|

{2,3}

|

true

| "a1:b2:c3:d4:e5:e6"

|

1

| {2}

|

0

|

1

|

ISCRITICAL column : When this field is set, the configured entry is

treated as rate-constrained or time-triggered; if this field is

cleared, the configured entry is a static configuration of a

best-effort flow and is treated as best-effort.

PORT Column value used for BE packets reaching here.

VL POLICING Table

This table provides timing and sizing rules for critical traffic.

TT

|

MAXLEN

|

SHARINDEX

| BAG

|

JITTER

|

true

|

2043

|

0

| 5

|

100

|

MAXLEN column : This field defines the maximum length of frames of this

entry in bytes including all Ethernet overhead (6-byte destination MAC

address, 6-byte source MAC address, 2-bytes EtherType field, 4-byte

frame checksum). The maximum allowed value for this field is 2043.

BAG Column : The bandwidth allocation gap (BAG) value to be used for this entry in multiples of 100 micro seconds.

JITTER Column : The bandwidth allocation gap (BAG) jitter value to be

used for this entry in multiples of 10 micro seconds. The value

provided for this field must not be larger (in seconds) than the value

provided for the BAG field. For example, if the value of BAG was 5, the

maximum allowed value for JITTER would be 50.

VL FORWARDIING TABLE

The following shows the layout of an entry in the VL Forwarding table.

SHARINDEX

|

TYPE

|

PRIORITY

| PARTITION

|

DESTPORTS

|

0

|

true

|

1

| 1024*1024

|

{2}

|

DESTPORTS column specifes the destination egress ports to which packets are forwarded to.

TYPE column value has to be true for time critical packets.

Scan Order Table

The following is the layout of an entry in the Scan order table:

PORT

|

Scan_Order

|

0

|

{0,1,2,3,4,5,6,7}

|

For each port, we can specify the order for polling the Queue Priority.