Code File Location: VisualSim/actor/arch/Buses/AMBA_AHB

2. Description

7. AMBA_AHB_Specification_and_Comparison_to_Model

8. Model_Parameters, Data Structure Fields and Ports

o The Advanced High-speed Bus (AHB) library block conforms to the ARM Advanced Microcontroller Bus Architecture (AMBA) specification for read, write, Retry and Split operations.

o

The

Advanced Microcontroller Bus Architecture was introduced in 1996 and is

widely

used as the on-chip bus for ARM processors. The first generation of the

AMBA

buses was the Advanced System Bus (ASB) and Advanced Peripheral Bus

(APB).

The VisualSim AHB Bus emulates the AMBA 2.0 AHB Bus Protocol to match the functionality and timing.

The AHB bus model has the following features:

- single edge clock protocol

- split transactions

- multiple bus masters and slaves

- burst transfers

- Retry transaction

- Wait states

- Single outstanding transaction

- pipelined address phase operations

- single-cycle bus master handover

- large bus-widths (64/128 bit)

Devices

The block contains 4 default Master and 4 default slave ports.

Transaction

The most common transaction sent through the AHB Bus is the Processor_DS. The bus uses the following fields of the Processor_DS:

The fields of the Processor_DS data structure determines the type of Transaction – Read or a Write, transfer size in bytes, split, source and destination.

Masters

and Slaves

The Master can be a standard block such as a DMA, Processor, traffic generator or a custom block that uses the DeviceInterface block as the protocol interface between the Block and the Bus. Similarly, the slave can be a Cache and DRAM or any other custom block that is connected to the Bus using the DeviceInterface block as the protocol interface. For the Slave side, the direction of the ports of the DeviceInterface block must be changed using the Right-click->Appearance->Flip Ports Horizontally.

Every Master and Slave is associated with a FIFO Buffer. The size is determined by the FIFO_Buffer parameter. The FIFO buffer is store the requesting or responding transaction that are waiting for the arbiter to allocate the bus.

Operation

On receiving a Processor_DS from the Bus Master, the transaction is placed in the FIFO Buffer and a request is sent to the Bus Controller. When the bus is available, the BusArbiter selects the master to grant access to the bus.

The

bus arbiter has two standard policies

to select the next Master to transmit- First Come-First Serve (FCFS)

and Round

Robin. The FCFS orders the incoming request in the order of

arrival and

based on the priority. The transaction priority is the value

in the A_Priority

field. Higher the value means higher the

priority. The Round-Robin gives equal weightage

to

all Masters and selects a transaction from each Master in order.

The

order of the Masters to transmit is listed in the parameter- "Round

Robin

Port Array" and allows transfer through the bus to the respective

slave.

Only one Master can be active on the bus at any time. Until

the bus

completes the transaction ie

the request and data

transfer, no other Master can gain Bus access. The lone

exception is a

When the next Master is selected, the Bus generates a single cycle for the Address and Control phase. The single cycle does not output any data structure. It generates a delay internally and the timing diagram will display the address cycle. The Bus Controller manages all commands and transfer on the Bus. The Bus Controller handles the response from the slave (proceed, or Split Transaction) and processes till the transfer completes. Only one outstanding transaction can be active on the Bus. The only exception is when a split transaction occurs. For more details on the split transaction, review the section below on Split Transaction.

Adding

Wait Cycles

It is

possible to add Wait states at any

time and to any transaction. The User can add “AHB_Cycles”

for any transaction entering the AHB Bus, and it will delay processing

for this

amount of Time. The user must add this field and specify the

value before

entering the AHB Bus block. If the field does not, exist, no

additional

Wait States are added. This process can also be used to add

additional

Wait States for a

Pipelined

Address Operation

Address Pipelining provides increased throughput to the AHB Bus by hiding the Address phase of the next transaction during the Data phase of the previous transaction. When there are multiple transaction to be sent out, the first transaction alone sends a Address Out. The first transaction is determined when the transaction starts from an empty request queue. When a new request is selected and there is an outstanding request, the transaction skips the address cycle and goes directly to sending the request.

Determining

the Availability of a

Slave Device

AHB Bus automatically identifies the state of the DRAM and Cache block and generates a Retry sequence if they are busy. Busy for these blocks is when the input Queue is full. For all other devices and for custom user devices, status of the destination can be referenced in a memory related to the final destination. If the value in the A_Destination field is “MyDevice”, then the status is checked at “MyDevice_Status”. "MyDevice_Status" must be a global memory. If true, the transaction would continue, else a retry would begin to execute. If no global memory is found matching this name, the AHB Bus assumes the status to be true.

When a

transfer occurs the slave can

decide to issue a

The

basic stages of a

Retry Operation

The RETRY response works only for Read operations. It currently does not support Write operations. It provides a mechanism for slaves to release the bus when they are unable to supply data for a transfer immediately. The mechanism allows the transfer to finish on the bus and therefore allow a higher-priority master to get access to the bus.

If the Cache or DRAM is used, the block uses the getBlockStatus RegEx to determine the status. For any other Destination, the Bus will check the global memory called Destination Name + "_Status". If the value of the RegEx or this Global Memory is true, the normal transfer occurs. If the value is false, then the Bus will generate a Retry. When a Retry occurs, the arbiter will continue to use the normal priority scheme and therefore only masters having a higher priority will gain access to the bus.

Adding

Additional Masters and Slaves

Additional Master and Slave ports can be constructed by doing the following:

Note:

AHB does not support “Custom” arbitration-mode. A error will be reported if the Custom is selected for the AHB Block.

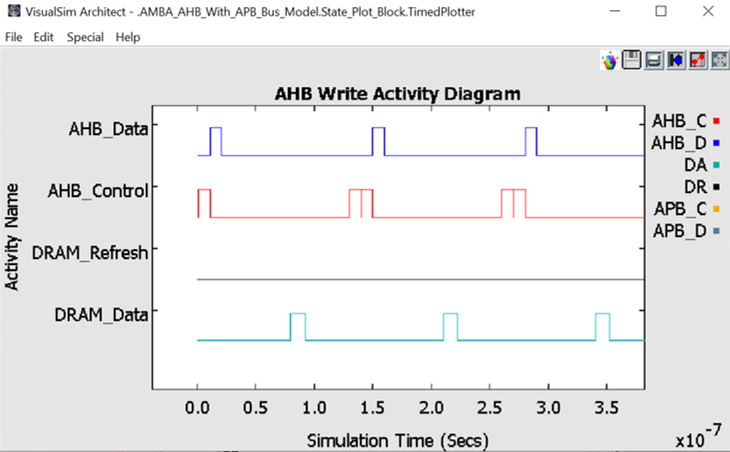

A Write transaction proceeds as follows.

Figure 1. Timing Diagram – Write Transaction

Data

Transfer – Write Transaction:

{A_Bytes, A_Command}

Address/Control

Signal:

First

fragment: {4,

Write} // sends address, 4 bytes (Bus Width), but A_Bytes will contain the original request size

-- corresponds to Bus Control (BC) trace in red.

Data Transfer:

Write

transfer: {64,

Write} // sends words, 64 bytes, output is sent

at the 1st word transfer and the remaining bytes are delayed internally.

The following table shows an example of a Write activity:

|

List of Fields |

Input from Master to Bus |

Output to Slave (End of all bursts) |

|

A_Bytes |

Request Data Size |

Value unchanged |

|

A_Destination |

Final Destination |

No Change |

|

A_Source |

Original Source |

No Change |

|

A_Interrupt (Opt.) |

FALSE |

No Change |

|

A_Prefetch (Opt.) |

FALSE |

No Change |

|

A_Status |

Used internally by Linear Bus. Set to Slave port name. |

Set to Slave port name + Append "_" |

|

A_Hop |

Slave side port name |

Next Bus, else Destination if direct connect |

|

A_Command |

Write |

No Change |

Table 1. Write Activity

The following table shows an example of a Write Response:

|

List of Fields |

Input from Slave |

Output to Master |

|

A_Bytes |

Request Data Size |

Value unchanged |

|

A_Destination |

Final Destination |

No Change |

|

A_Source |

Original Source |

No Change |

|

A_Interrupt (Opt.) |

FALSE |

No Change |

|

A_Prefetch (Opt.) |

FALSE |

No Change |

|

A_Status |

This is used internally by the Linear Bus. This is set to Master port name |

Append _ to_Name |

|

A_Hop |

Don’t Care |

Next Bus or Destination if direct connect |

|

A_Command |

Read. Can have any suffix |

Unchanged |

Table 2. Write Response

A Read transaction proceeds as follows.

Read Request Transaction:

Note: The Read transaction takes one cycles to send the the packet out.The following table shows an example of a Read Request Transaction:

|

List of Fields |

Input from Master |

Output to Slave |

|

A_Bytes |

Request Data Size |

Value unchanged |

|

A_Destination |

Final Destination |

No Change |

|

A_Source |

Original Source |

No Change |

|

A_Interrupt (Opt.) |

FALSE |

No Change |

|

A_Prefetch (Opt.) |

FALSE |

No Change |

|

A_Status |

This is used internally to set the Master port name |

Append _ to Name |

|

A_Hop |

Don’t Care |

Next Bus or Destination if direct connect |

|

A_Command |

Read. Can have any suffix |

Unchanged |

Table 3. Read Request Transaction

Read Transaction- Response:

Note: The Read response takes two cycles to send the the packet out, 1 cycle for address/control and another cycle for 1st word transfer. The remaining values are delayed internally.

The following table shows an example of a Read Transaction- Response:

|

List of Fields |

Input from Slave |

Output to Master (End of all Bursts) |

|

A_Bytes |

Request Data Size |

Value unchanged |

|

A_Destination |

A_Source (Names flipped from Request. Can be an alternate destination also) |

No Change |

|

A_Source |

A_Destination (Names flipped Request.) |

No Change |

|

A_Interrupt (Opt.) |

FALSE |

No Change |

|

A_Prefetch (Opt.) |

FALSE |

No Change |

|

A_Status |

Used internally. Set to Slave port name |

Set to Master port name + Append "_" |

|

A_Hop |

Slave side port name |

Next Bus or Destination if direct connect |

|

A_Command |

Write |

No Change |

Table 4. Read Transaction- Response

Figure 2: Timing Diagram – Read Transaction

Data Transfer – Read Transaction

{A_Bytes, A_Command}

Address/Control

Signal:

First

fragment: {64,

Read}

//sends address, 4 bytes(Bus Width), but the A_Bytes maintain the original request size

-- corresponds to Bus Control (BC) trace in red.

Data

Transfer:

The slave DRAM reads and returns the read data, setting the A_Command as ‘Write’.

The

64 bytes to be transferred through

the bus are sent from the Slave device.

Write

transfer: {64,

Write} //sends words, 64 bytes, output is issued

after the 1st word transfer, remaining bytes are delayed internally.

-- corresponds to Bus Data (BD) trace in blue.

The

Read response returning to the Master

is sent when all of the data has been received. On receiving a Processor_DS from the Bus

Master, the

Following are the list of demo models available in the tool.

VS_AR/doc/Training_Materials/Architecture/Bus/AHB_AXI:

1.

AHB_Buffered_Non_Buffered.xml

2. AHB

_MultiMaster_Fabric.xml

3.

All_AHB_Bus.xml

4.

AMBA_AHB_Bus_Model.xml

5.

AMBA_AHB_with_APB_Bus_Model.xml

6.

linear_Bus_AHB_Split2_Read_Test.xml

7.

Linear_Bus_AHB_Split2_Read_Write_Test.xml

8.

linear_Bus_AHB_Split2_Write_Test.xml

9.

AHB_AXI_Bus.xml

10.

AHB_APB_Bus.xml

11.

Smartfusion_test2.xml

12.

Three_level_Bus_Model.xml

Before an AMBA AHB transfer can commence the bus master must be granted access to the bus. This process is started by the master asserting a request signal to the arbiter. Then the arbiter indicates when the master will be granted use of the bus. A granted bus master starts an AMBA AHB transfer by driving the address and control signals. These signals provide information on the address, direction and width of the transfer, as well as an indication if the transfer forms part of a burst. A write data bus is used to move data from the master to a slave, while a read data bus is used to move data from a slave to the master. Every transfer consists of:

The address cannot be extended and therefore all slaves must sample the address during this time. The data, however, can be extended using the HREADY signal. When LOW this signal causes wait states to be inserted into the transfer and allows extra time for the slave to provide or sample data. During a transfer the slave shows the status using the response signals, HRESP[1:0]:

OKAY

The OKAY response is used to indicate that the transfer is progressing normally.

In the VisualSim model, normal progress does not require a response.

HREADY

HREADY goes HIGH this shows the transfer has completed successfully.

In the VisualSim model this corresponds to the data structure returned, no interpretation is necessary.

ERROR

The ERROR response indicates that a transfer error has occurred and the transfer has been unsuccessful.

In the VisualSim model, errors do not occur due to noise or hardware failure.

RETRY

and

Both

the RETRY and

In normal operation a master is allowed to complete all the transfers in a particular burst before the arbiter grants another master access to the bus. However, in order to avoid excessive arbitration latencies it is possible for the arbiter to break up a burst and in such cases the master must re-arbitrate for the bus in order to complete the remaining transfers in the burst.

To Run the Model, the Model Parameters and the transaction data structure flowing into the respective channel of the AHB Bus Block (ex: Processor_DS) etc need to be setup.

|

Parameter Name |

Value (Data Type) |

Explanation |

|

Architecture_Name |

“Architecture_1”(String) |

It

refers the Architecture_Setup name. Please keep both the names as same.

It can be linked to top level parameter. Giving different names other

than Architecture_Setup block's name will throw an error. |

|

Bus_Name |

“AHB” (String) |

Unique name for this Bus. This name must be different from all architecture blocks, schedulers, smart_resources and global model memories. |

|

Enable_Plots |

false (check box) |

This parameter is used for enabling the activity plotter for AHB. It will give the Timing diagram for each ports based on the control/Address and Data transaction within the bus |

|

FIFO_Buffers |

8(int) |

It defines the input Buffer size of the bus. It can be linked to top level parameter. If the number of input request coming to the bus is higher than FIFO Buffer length, then some of the packets can be lost. |

Key parameters for configuration

|

||

|

Bus_Speed_MHz |

100.0 (Double) |

Speed of the bus is specified in terms of Mega Hertz. This

value is used for defining the clock cycle and internal timings. It can be

linked to top level parameter. |

|

Bus_Width_Bytes |

8 (Int) |

This parameter defines the width of the bus. The Bus can transfer only this much bytes in a single clock cycle. |

|

Burst_Size_Bytes |

16 (Int) |

It defines the Maximum length of Bytes that the bus can send as burst transfer. Burst size should be greater than Bus_Width_Bytes. This parameter can be linked to top level parameter. If A_Bytes that is equal to or smaller than this number will be sent as a single burst. Any A_Bytes that is greater than this number will become two or more bursts. |

|

Round_Robin_Port_Array |

{Bus_Name+"_Port_1", |

This parameter can be used only when the bus operates on Round Robin mode. It determines the Round robin order for the ports. |

|

Device_Attached_to_Slave_by_Port |

{"Device_1"}, {"Device_2"}, {"Device_3"}, {"Device_4"}, {"Device_5"}, {"Device_6"}, {"Device_7"}, {"Device_8"}} (Array of Strings) |

This parameter can be used for routing purpose when the hello messages are disabled. It will help the bus to transfer input data to a specific destination port. |

|

Mode_Arbiter |

FCFS (Pull-down) Available options: FCFS, RR, CUSTOM |

This parameter defines mode of AHB Bus. FCFS defines

the First Come First Serve mode and RR defines Round Robin mode of operation CUSTOM is

the option used for implementing custom Scheduling algorithm for AHB

Master and Slave ports. It can be achieved by using custom_out,

custom_in ports in AHB. |

Table 5: List of AHB Bus Block Parameters

|

Data Structure Field |

Value (Data Type) |

Explanation |

|

A_Bytes

(necessary) |

100 (Int) |

This is the total bytes to be transfered for this transaction. All bursts of this transaction will have this value. |

|

A_Bytes_Remaining |

96 (Int) |

The number of bytes remaining after the current transaction. |

|

A_Bytes_Sent |

4 (Int) |

The number of bytes in this transaction. |

|

A_Command (necessary) |

"Read" or "Write" or "Read_Split" (String) |

This determines the operation. |

|

A_First_Word |

true or false (Boolean) |

Specifies whether this is the first word of the transfer |

|

A_Priority |

2 (Int) |

This is priority of the transaction. The transactions waiting for service are reordered based on this value. |

|

A_Source (necessary) |

"Processor" |

This is unique name of the Source. When the transaction returns from the Destination, the Source and Destination names are flipped. So, the Source becomes the Destination and Destination becomes Source. |

|

A_Destination (necessary) |

“DRAM” (String) |

Final Destination |

|

A_Hop |

“DRAM” (String) |

Set to match A_Destination |

|

A_Task_Flag |

false (Boolean) |

The default is false, which means that the Master does not require an acknowledge for a Write. If set to true, the VisualSim standard blocks will send a acknowledgment back when all the data has been written to the Slave. The DMA block uses this field to get a return from the Cache or DRAM block. |

Table 6: List of Data Structure Fields used in the AHB Bus

|

Port Name |

Type |

Explanation |

|

port1, port2, port3, port4, port5, port6, port7, port8 |

Multiport or input/output. Connection must be made in order- first input to this port and then output away from this port. |

Each port is for a Master or Slave. Transaction Data Structure of type Processor_DS. |

Table 7: List of AHB Bus Ports

|

Description |

A_Command |

A_Bytes |

A_Bytes_Remaining (optional) |

A_Bytes_Sent (optional) |

|

100 Byte Read at Slave. Bus Width = 4 |

Read |

100 |

96 |

4 |

|

100 Byte Read Return at Master |

Write |

100 |

0 |

100 |

|

100 Byte Write at Slave |

Write |

100 |

0 |

100 |

Table 8: Transation Field Values

The following image shows the right way to connect the AHB in the Architecture. Source like Processor and DMA can be connected directly to the AHB port, but if the Master device is designed with simple library block(as logic) then user has to include Device Interface block to provide the interface with master. Similarly for Slave. Slave like RAM, Integrated cache and display can be connected directly to the slave port.

The

Bridge block plays important role in connecting the different buses in

the architecture. Two buses can not be connected directly, user has to

use Bridge block.

The Key statistics for the AHB bus are:

1. Delay

The maximum and minimum delay that is handled by the AHB during the simulation.

2. IO operations per second

The total number of input and output operations happened during the simulation

3. Input Buffer Occupancy

Whenever the bus is occupied the input requests will be waiting in the buffer.

4. Preempt Buffer Occupancy

The request that are preempted by the higher priority request are

5. Throughput

Throughput of the bus in terms of Mega bytes per second are observed.

6. Utilization

Percentage of utilization for this bus is observed for the entire simulation time.

These are analyzed as max, min, mean and standard deviation of it.

The following image shows the statistics that can be observed and analyzed in AHB bus.

Analysis:

AHB Delay:

Bus Width bytes will determine the number of cycles

of delay other than control/address cycle in the internal process. User

can check whether the uniform transaction is happening or not based on

the model construction.

IO operations per second:

Number of IO operations in the consecutive blocks

should be same. if there are mismatching amount of transactions is

displayed then the block is not receiving the exact transactions from

the neighboring blocks.

Input Buffer Occupancy in words:

The buffer occupancy(number of words based on bus

width) of the bus during the simulation are observed, it will help the

user to determine the buffer length of the design during the actual

design integration.

Preempt Buffer Occupancy:

This will help the user to analyze the number of

request that is buffered in the queue because of the preemption of

higher priority request.

Throughput:

This will help the user to check whether the

designed speed and bytes are working properly or not. Throughput can be

compared with the neighbor blocks to check whether the requests are

processed by the bus during the simulation or not.

If the throughput is not same as the neighbor blocks

then check the connectivity or the previous block to see the data is

routed properly. Some ports may not be connected and the data are not

getting processed.

Utilization:

This will help the user to see how good the

resources are utilized in the design. Based on the percentage of

utilization user can improve the system configuration to get efficient

outcomes.

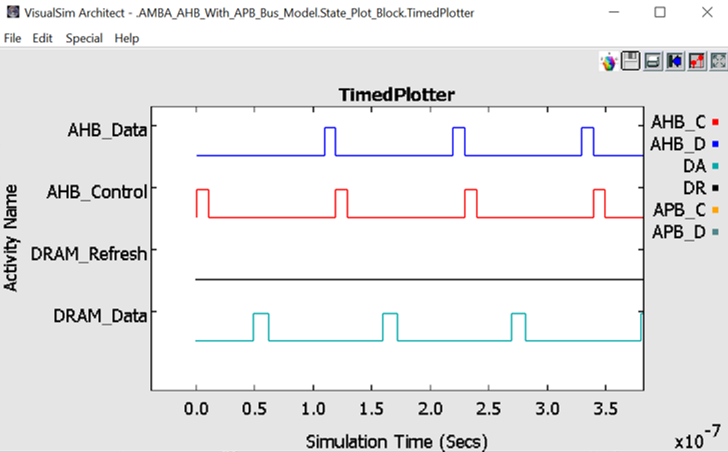

There are two methods for enabling and analysing the plots in the AHB bus.

1. Adding Timing daiagram to the model (Hardware Setup - >

TimingDiagram) and modify the bus name in the configuration window.

This will shows the overall transaction in the bus along with the other

blocks in the model.

2. Enabling the "Enable_plot" parameter in AHB configuration window.

This will show the data transaction at each port.

1.

Explanation : if

(port_token.A_Command == "Write") false, expression plus 4, else plus

1., Check argument types, argument values, field names, and variables.

Exception :

VisualSim.kernel.util.IllegalActionException: No method found matching

{A_Bytes = int, A_Destination = string, A_Hop = string, A_Instruction =

arrayType(string), A_Source = string, BLOCK = string, DELTA = double, DS_NAME =

string, ID = int, INDEX = int, TIME = double}.A_Command()

2.

VisualSim.kernel.util.IllegalActionException:

.AHB_Testing.AMBA_AHB.AMBA_Port @ 0.0 ps -->

Created with the Personal Edition of HelpNDoc: Free Kindle producer