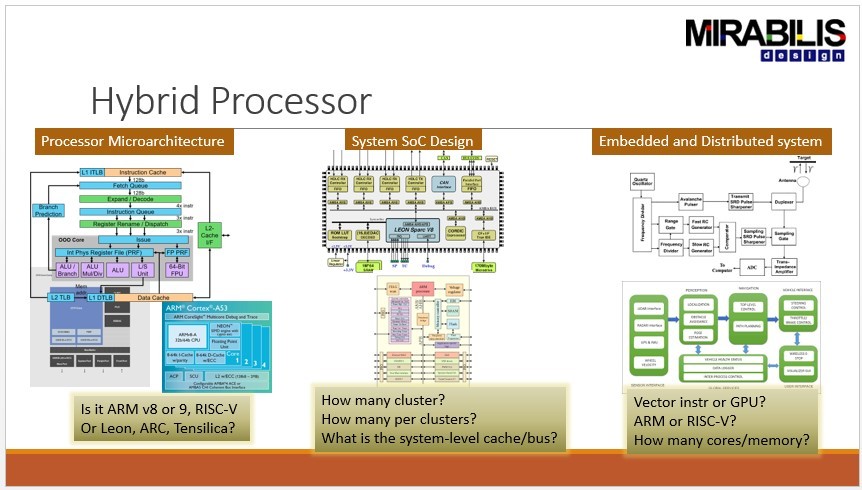

Recently introduced by Mirabilis Design, the hybrid processor is an enhancement to the company’s IP library. This is a big leap for those working with either new processors, or with a combination of processors of different sets like Tensilica, Arm and RISC-V.

Earlier Mirabilis Design had a different model for each processor and for each level of analysis and abstraction. With the hybrid processor, a single IP component can be reused for all the analysis from stochastic to cycle-accurate by varying parameter values.

The Hybrid Processor is a Processor IP Generator for system modeling and validation. The IP will run at the speed of stochastic but with the detail of a cycle-accurate processor. In today’s world, multiple stages of the design process require system models. There is the conceptual designer, R&D engineer, development architect, the marketing people, and the system designer that will integrate this IP or System-on-Chip (SoC) into a distributed system.

The commonality among all of these users is, the models are needed for validation. The interfaces are common, the sensors or the input wire or Ethernet are common; the output – which is an egress port connected to the internet, display or instrumentation panel.

What Mirabilis Design has done with the hybrid processor is that same models are allowed to be reused across the design process.

Some of us could perhaps respond to this with, ‘Hey, that’s not a big deal, If I have this thing in C++, I could do it very easily.’

The answer to that is actually yes and no! Models used at these different levels for the SoC internals, tends to be completely different. Interfaces are completely different, the structures or what are called the transactions, are completely different.

With the Hybrid Processor model, Mirabilis Design has created a stochastic model for a concept engineer transaction-level model for a development engineer a cycle-accurate model for the validation and testing team, and a model to integrate with a high-performance computing or distributed system.

The interesting thing is that all of them have the same interface. So one can be swapped with another.

Additionally, these models have different levels of data available. If no software is available, there is a profile-based software generator that can be used. If the cache address is not available, Mirabilis Design has a tool that intelligently generates the addresses based on the profile of the software. Thus, there is a whole umbrella of items that has been created, which can be utilized by anyone building a new SoC, including the facility to be able to choose what is required from the available library of IPs.

Have a question? Or would like to know more? Do let us know!