Quick Explanation

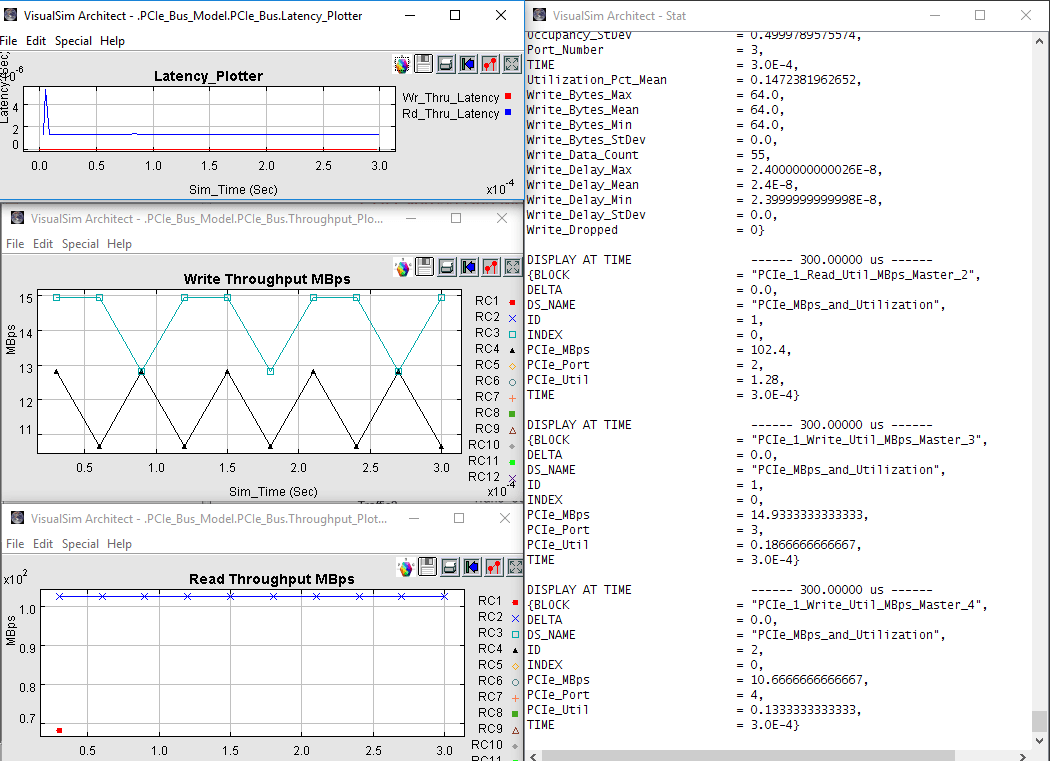

- Supports generation of bus statistics

- Supports block debug feature

- Supports flow control for root complex and end point

Protocol

- v. 1.x (2.5 GT/s): 250 MB/s (×1) 4 GB/s (×16)

- v. 2.x (5 GT/s): 500 MB/s (×1) 8 GB/s (×16)

- v. 3.x (8 GT/s): 985 MB/s (×1) 15.75 GB/s (×16)

- v. 4.x (16 GT/s): 1.969 GB/s (×1) 31.51 GB/s (×16)

- v. 5.x (32 GT/s): 3.938 GB/s (×1) 63 GB/s (×16)

Model Link

Overview

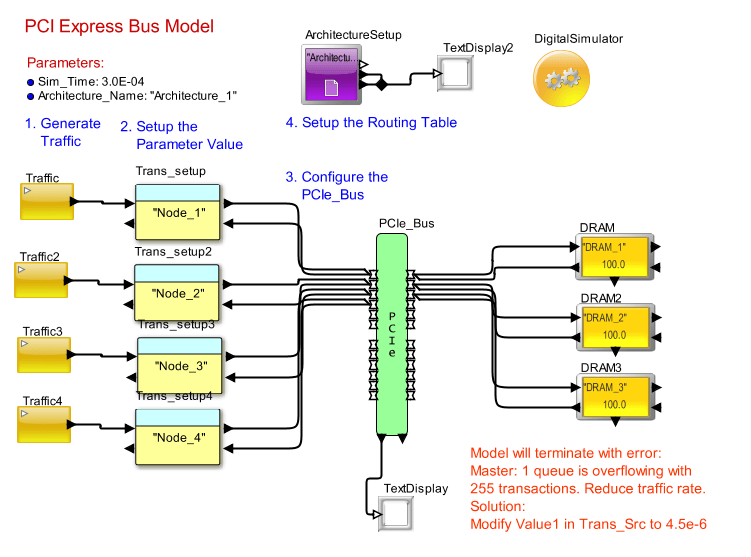

VisualSim Peripheral Component Interconnect Express (PCIe) is a comprehensive modelling library that encompasses the entire PCIe 3.0 protocol published by the PCI-SIG. The PCIe block can be connected to processors, memory, FPGA, SSD, disks, caches, I/O and a host of other devices available in the VisualSim hardware library. The model can be simulated to evaluate the performance bandwidth, determine the number of connected devices and fine-tune the PCIe attributes. The model can be used to study the impact of PCIe implementation from different semiconductor vendors, and design the implementation for FPGA and ASIC. The library contains the bridges required to integrate the PCIe to Gigabit Ethernet, AXI and, a number of other buses and networks. The library can be used to model the PCIe system for server, industrial, and consumer applications. The completeness of the PCIe and the extended hardware/software architecture library allows a designer to view the operation of the entire high-performance system.

VisualSim PCIe library models the entire bus protocol in accurate detail. The model can be simulated with statistical traffic or a real trace from an existing system. The timing accuracy of the PCIe internals enables the same library to be used to debug PCIe systems in the field.

Parameters used

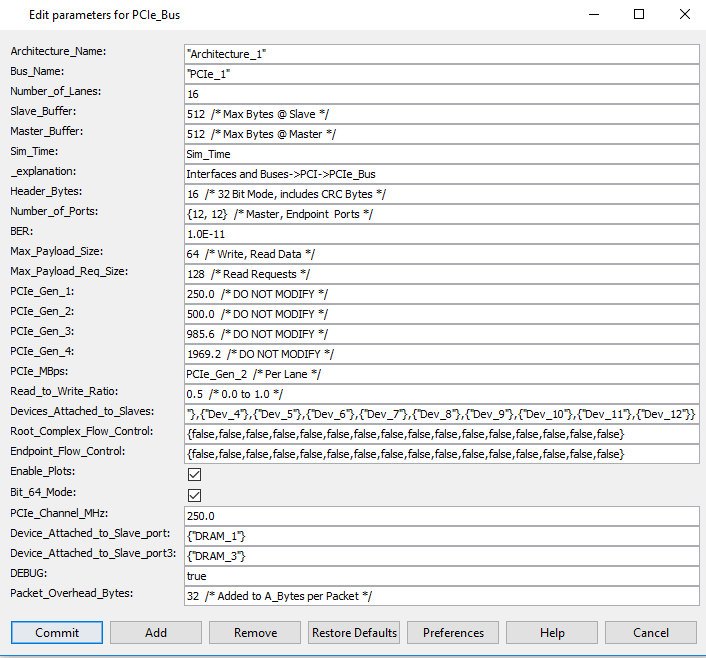

The PCIe bus is a high-speed serial replacement of the older PCI/PCI-X bus, an interconnect bus using shared address/data lines. Library can support any form of topology and also support integration with other point-to-point, serial, parallel and shared buses and protocols. The block is parameterized for data burst sizes, number of channels, speed per channels, flow control and connected devices. There are separate serial links connecting every device to the root complex (host). Bus link supports full-duplex communication between any two endpoints, with no inherent limitation on concurrent access across multiple endpoints. The VisualSim PCIe block communication is encapsulated in packets or data structures. The work of packetizing and de-packetizing data and status-message traffic is handled by the transaction layer of the PCIe port, which is inside the bus block.

- Number_of_Lanes: This can be single value or an array of the number of master

- Header_Bytes: This is the packet header size

- Number_of_Ports: Used for expansion

Features

Some of the features of the PCIe block used in VisualSim are as follows:

- Block debug feature, this enables the user to visualize the active transaction, current time and channel.

- The PCI Express library comprehends future performance enhancements via speed upgrades advanced encoding techniques.Generation of bus statistics. Throughput in Mbps, Bus utilization in percentage, Input/Output transactions/sec, Root complex buffer occupancy and End point buffer occupancy values.

- Block debug feature, this enables the user to visualize the active transaction, current time and channel.

- User can apply flow control for root complex and end point.

In General

The PCI Express(PCIe) provides a scalable, high speed, serial I/O bus that maintains backward compatibility with PCI applications and drivers. The PCI Express layered architecture supports existing PCI applications and drivers by maintaining compatibility with the existing PCI model. PCI Express have parallel bus topology and multiple point-to-point connections. A switch may provide peer-to-peer communication between different endpoints and this traffic. A PCI Express link consists of dual simplex channels, each implemented as a transmit pair and a receive pair for simultaneous transmission in each direction. Each pair consists of two low-voltage, differently driven pairs of signals. A data clock is embedded in each pair, using an 8b/10b clock-encoding scheme to achieve very high data rates.