Architecture exploration and performance analysis of RapidIO Based System Architecture

Introduction

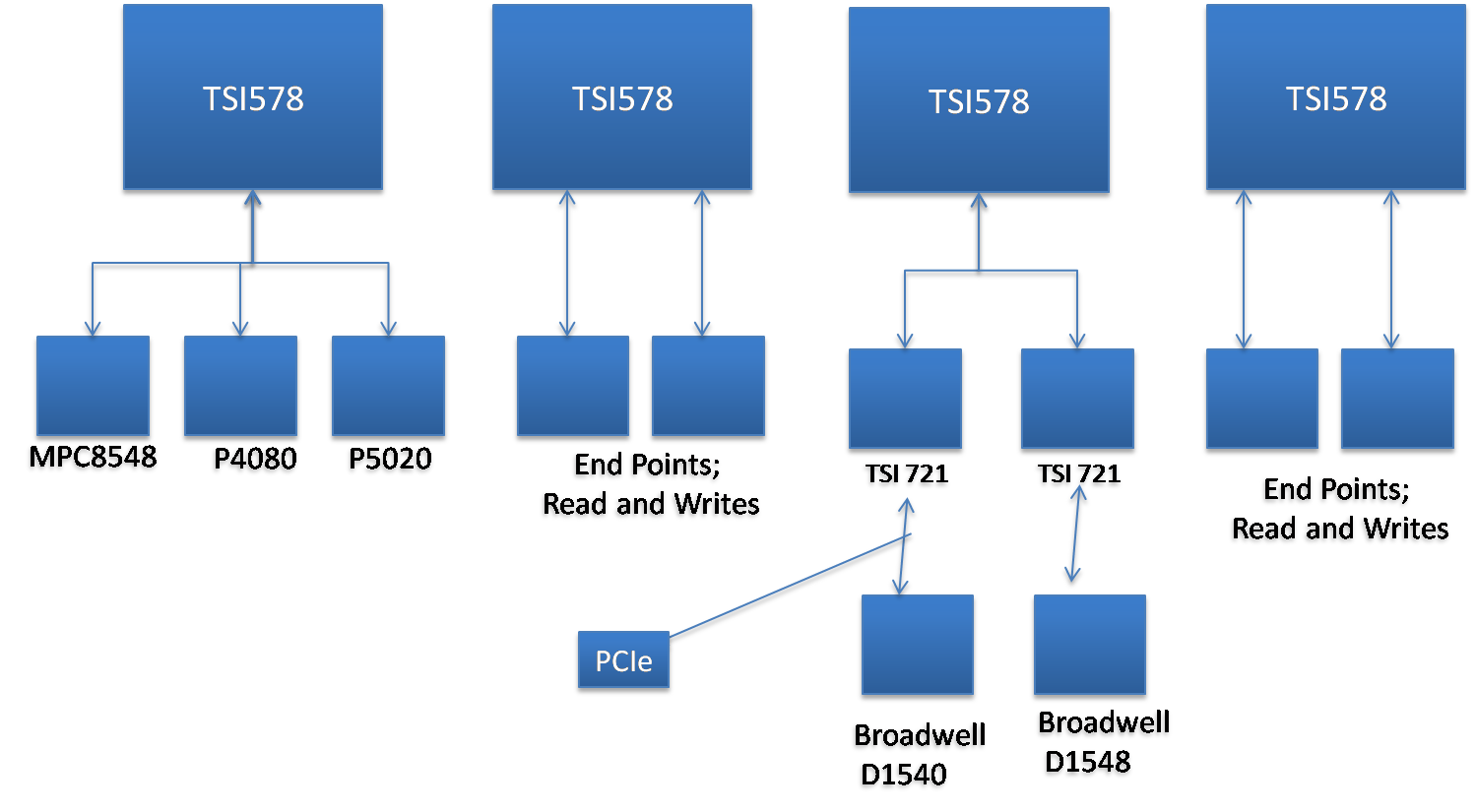

Purpose of this modeling experiment was to explore a Freescale PowerPC based System architecture connected over RapidIO switches. System architecture includes Freescale P4080, P5020, MPC 8548, Intel Xeon Processors and RapidIO Switches from IDT and PCIe RapidIO Bridge. All the components are part of VisualSim Modeling Library set and are completely configurable to easily switch between different flavors of Processor, memory and RapidIO Switches.

Block Diagram of the proposed system architecture is shown in figure below

VisualSim Model of the complete System is as shown below

To visualize and modify internal details of each processor modules, please right click on the block and select Open Block from the right context menu. RIO Switches and Nodes are configurable and to change configurations please double click on the block and change the configurations based on user requirements.

Combination of RIO Nodes and Serial Switches will provide the right configuration for a RIO Switch and for the purpose of system exploration and for customization we have adopted the approach of splitting RIO Node and Serial Switch. If the user would require exact RIO Switch Library, then Mirabilis Design will provide the libraries.

In the VisualSim model shown in figure2, Blocks connected to Serial Switch 1 at the left hand side are Freescale Processors, Blocks connected to Second Switch from left are custom RIO End Systems performing Read/Write Operations. The third switch from left is connected to a RIO PCIe Bridge which intern connected to Xeon Broadwell processors over a PCIe Bus. Forth Switch from the left is connected to custom RIO End Systems.

Behavior Flow

As we were not sure about the application data flow we have implemented the application behavior flow in a generic approach. Each Processor modules initially perform boot loader application and get the data/instructions from remote memory. Once the Process is over Processor starts processing application specific instructions generated using VisualSim Profiler based Instruction generator. Interesting part about VisualSim Software generator is that, even if the user is not having application software ready and if the topology or resources for the hardware architecture is not yet decided then the Software generator generating instructions to replicate real application running on the platform with very minimal information.

Results and Analysis

Please run the model with default configurations, the reports generated are MIPS for P4080, P5020 and MPC8548 processors, application latency across processors, Latency across PCIe bus and RIO Message details. Results are provided in both graphical and textual format, based on user requirements custom reports can also be generated. Few Reports generated are shown below