The following has been considered while modeling :-

|

STATE |

OFF |

SLEEP |

2G |

3G |

|

PLL |

OFF |

ON |

ON |

ON |

|

CLKMUX |

OFF |

SLEEP |

2G |

3G |

|

2G |

OFF |

OFF |

ACTIVE |

SLEEP |

|

3G |

OFF |

OFF |

SLEEP |

ACTIVE |

|

PROC |

OFF |

IDLE |

2G |

3G |

|

BAT |

1,0 |

1,0 |

1,1 |

1,2 |

|

LDO |

ON |

ON |

ON |

ON |

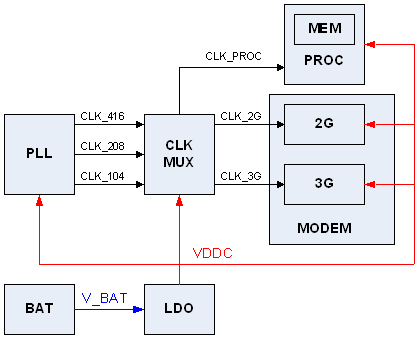

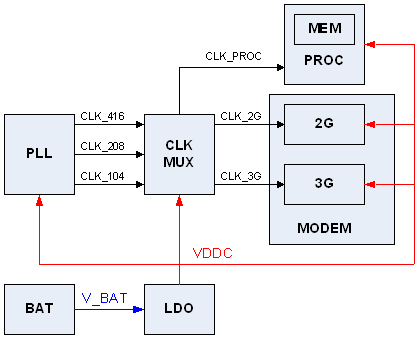

2G Block: states: ACTIVE,SLEEP,OFF | 3G Block: states: ACTIVE,SLEEP,OFF |

| PROC: states: 3G,2G,IDLE,OFF active current: clk_i*VDDC*NDP(3G,SLEEP)+I_access_mem static current: area*LBV(VDDC)+I_leak_mem+I_leak_switch(VDDC) (for off mode only I_leak_switch) Area:3,2mm² and 2000 switches | PLL: states: ON,OFF active current: I_act(ON) ; (fixed val per state) static current: fix val(VDDC) |

| LDO: states: ON,OFF I_housekeeping = no_load_current + eff_factor*Iload I_drawn = Iload + I_housekeeping | CLKMUX: States: 3G(clk_2G=104, clk_3G=208, clk_PROC=416Mhz) active current: I_act(3G,2G,SLEEP,OFF) ; (fixed value per state)2G(clk_2G=208, clk_3G=104, clk_PROC=208Mhz) SLEEP(clk_2G=0, clk_3G=0, clk_PROC=104Mhz) OFF (all clks=0) static current: fix value(VDDC) |

| NDP: Normalized Dynamic Power (µA/Mhz/V) Variable | 1,0V 3,0E-11 | Switch leakage (per switch) 1,1V 3,5E-10 1,2V 6,0E-10 |