Architecture Exploration of ARM-based SoC and Chiplets using VisualSim

Learn to explore semiconductor architectures with VisualSim Architect—the exclusive public provider of architecture models for ARM v8/v9 processors and other ARM IPs including Corelink-Cyprus, AMBA AXI/CHI, GPU, DMA, DSU, and additional critical IP blocks. This webinar is designed for engineers and architects aiming to master advanced performance and power analysis techniques for both monolithic and chiplet-based SoCs, with a special emphasis on supporting ARM CHI and C2C interconnects.

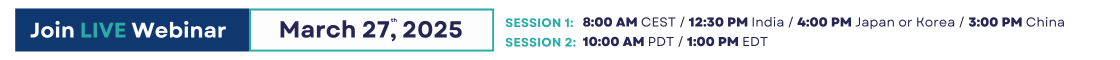

Session 1: 8:00 AM CEST / 12:30 PM India / 4:00 PM Japan or Korea / 3:00 PM China

Register- https://us06web.zoom.us/meeting/register/7rsjb2dIS4Ss9j4ac-eeZw

Session 2: 10:00 AM PDT / 1:00 PM EDT

Sign Up- https://us06web.zoom.us/meeting/register/_s0LUGrLSiuDR8qTNrb2HQ

Key Technical Highlights:

- Comprehensive Architecture Modeling:

Discover how VisualSim Architect’s cycle-accurate SoC models enable precise simulations of ARM v8/v9 cores and integrated IP blocks. Understand the underlying architecture, including those for Corelink-Cyprus and AMBA CHI, that are crucial for next-generation SoC design.

- System-Level Modeling for Monolithic & Chiplet Architectures:

Learn the methodologies to construct scalable system-level models. The webinar will cover how to compare and partition as the user transitions from monolithic designs to chiplet-based architectures, ensuring robust support for ARM CHI C2C interconnects.

- Dataflow Visualization & Performance Debugging:

Gain insights into advanced techniques for visualizing SoC dataflow. Attendees will explore how to debug performance issues by measuring key metrics such as latency, throughput, hit-ratio, and coherence overhead—vital for diagnosing system inefficiencies.

- Power Management & Optimization Strategies:

Learn to integrate power management features within your SoC models to reduce peak power and overall consumption. The session will detail strategies to optimize system topology for reduced latency and improved power efficiency, including identifying and resolving both performance and power degradations.

- Interconnect & IP Block Integration:

Get technical guidance on how to interconnect various IP blocks with Corelink CMN-Cyprus devices. The session will also showcase how to leverage the Socrates block diagram to quickly develop and validate VisualSim models.

- Processor Utilization in SoC Design:

Explore practical approaches to incorporate ARM Neoverse, A-, M-, and R-Series processors within your SoC design, ensuring optimal performance and resource allocation across different application scenarios.

Session 1: 8:00 AM CEST / 12:30 PM India / 4:00 PM Japan or Korea / 3:00 PM China

Register- https://us06web.zoom.us/meeting/register/7rsjb2dIS4Ss9j4ac-eeZw

Session 2: 10:00 AM PDT / 1:00 PM EDT

Sign Up- https://us06web.zoom.us/meeting/register/_s0LUGrLSiuDR8qTNrb2HQ