Memory / RAM

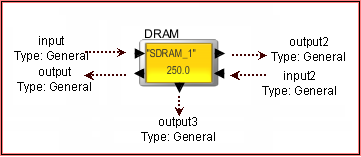

Block Name: RAM

Code File Location: VisualSim/actor/arch/DRAM

Table of contents

- Block Description

- Application

- Operation

- Expected fields

- List of Models

- Parameter configuration and ports

- Enabling plots

- Statistics

- Error messages and solution

Description

This block combines the operation of a basic memory controller (delay function) and the memory array.

The block handles pre-fetch, read, write, refresh and controller operations. The block can be interfaced to any Bus or Memory Controller. The incoming instructions are treated as Read request, Prefetch request, Write and Erase. All A_Command starting with Read are treated as Read operation. All A_Command starting with Write or Erase are treated as Write. A pre-fetch is a special case and is similar to a Read operation. The access time for each command type (Here it is the specific A_Command name) is defined in the Access_Time field.

Refer DRAM and Cache Demo Model.

Application

o ROM, RAM, SRAM, DRAM or SDRAM

o Synchronous Dynamic (SDRAM)

o Double Data Rate (DDR, DDR-2, DDR-3) SDRAM

o Quad Data Rate (QDR) SRAM

o Direct Rambus (DRDRAM)

o Video DRAM (VRAM)

o Synchronous Graphics RAM (SGRAM)

o Pseudo Static RAM (PSRAM)

o Disk Drive

o NAND and NOR Flash

Operation

The memory receives a request for a data or instructions. The request can come from either of the input ports. Note that this is not a dual-ported RAM. The two port connections are for convenience only and are connected to a single controller and array. The Memory block does not distinguish between Data and Instruction requests.

If separate memory devices needs to be assigned for Data and Instruction, then use two memory blocks.

If the Memory FIFO Buffer > 0, then multiple memory requests are queued and processed on First Come-First Serve basis.

The FIFO is common for both ports. Each request is delayed by a combination of one controller time + access_latency*request Size/width (A_Bytes)/Memory_Width. The incoming field A_Command contains the instruction name. All A_Commands starting with Read are treated as a read and a response is sent back on the output/output2 port respectively as A_Command=Write. A pre-fetch is a special case of a Read and a response is sent out as A_Command=Write. For a Write operation, there are two posisble conditions. If A_Task_Flag field is set to true, then the transaction is sent back as A_Command=Read to the source. If A_Task_Flag is set to false, then the transaction is sent out on output3. For a Read operation, the first word is sent out while for a write, the last word is send out. A DRAM refresh event is scheduled periodically. When the DRAM is in refresh state, the memory array and the controller delay cannot be executed. These requests are processed when the memory returns to the working state. A single transaction can have a multi-word request. The total transaction size is in A_Bytes and the individual word size is in A_Bytes_Sent.

Latency

There are two components to the memory latency- controller time and the access time. The controller_time is delayed for the first word of the entire transaction. It is not applied to each individual word. This value is given by the Controller_Time parameter and defaults to Cycle_Time. The Controller_Time parameter can be an expression that contains variables, fields of the incoming data structure, parameter, RegEx and any Expression line that is available in ExpressionList block. The Cycle_Time = (Controller_Ratio)/Memory_Speed_Mhz. The Controller_Ratio depends on the Memory_Type (SDR=1.0, DDR=2.0 and QDR=4.0). The Access_Time is specified for one Word_Width of memory. The total transaction will have a delay of A_Bytes/Memory_Width*Access_Time. If using DDR3, then the Access_Time = 1000.0/Memory_Speed_Mhz/2.0. If using SDR, then the Access_Time = 1000.0/Memory_Speed_Mhz/1.0.

Different Timings between Bus and Memory

The default operation of the DRAM is to send out the first Word and delay the rest of the data access internally. If the field A_Bytes_Remaining is set to 0 and A_Bytes_Sent = A_Bytes, then the last word is sent out. So, if the DRAM is slower than the Bus speed, add a DS_if_else_statement block between output of the Bus and input of the DRAM. The if-else statement will be "A_Destination != Architecture_Name", then add the first line statement to A_Bytes_Remaining = 0 and the second line to A_Bytes_Sent=A_Bytes. This demo example shows how this is done.

Expected Data strucutre fields

|

Data Structure Field |

Value (Data Type) |

Explanation |

|

A_Bytes

(necessary) |

100 |

This is the total bytes to be transfered for this transaction. All bursts of this transaction will have this value. |

|

A_Bytes_Remaining (necessary) |

96 |

The number of bytes remaining after the current transaction. |

|

A_Bytes_Sent (necessary) |

4 |

The number of bytes in this transaction. |

|

A_Command (necessary) |

"Read" or "Write" |

This determines the operation. |

|

A_Source

(necessary) |

"Processor" |

This is unique name of the Source. When the transaction returns from the Destination, the Source and Destination names are flipped. So, the Source becomes the Destination and Destination becomes Source. |

|

A_Destination (necessary) |

“DRAM” |

Final Destination |

|

A_Task_Flag (necessary) |

false |

The default is false, which means that the Master does not require an acknowledge for a Write. If set to true, the VisualSim standard blocks will send a acknowledgment back when all the data has been written to the Slave. The DMA block uses this field to get a return from the Cache or DRAM block. |

Input request combination

|

Description |

A_Command |

A_Bytes |

A_Bytes_Remaining |

A_Bytes_Sent |

|

100 Byte Read at Slave. Bus Width = 4 |

Read |

100 |

96 |

4 |

|

100 Byte Read Return at Master |

Write |

100 |

0 |

100 |

|

100 Byte Write at Slave |

Write |

100 |

0 |

100 |

Data Structure Fields

The A_Source, A_Destination, A_Command, A_Bytes, A_Bytes_Remaining and A_Bytes_Sent are the required field. Additional fields required are A_Hop, A_Status, A_Task_Flag, A_Interrupt, A_Prefetch and A_Priority. The A_Source and A_Destination are reversed before sending the response for a pre-fetch and Write/Read operation. The A_Command defines the access delay and the type of instruction. The A_Command value must match one of the items in the Access_Cycles parameter.

Additional information on this library block is available in Chapter 3 - Advanced Modeling Topics.

List of models

VS_AR\doc\Training_Material\Architecture\StorageCache_DRAM.xml

VS_AR\doc\Training_Material\Architecture\Bus

Read_Bus_Match_Bus_Memory_Timing.xml

VS_AR/Demo/Bus_Std/AHB_AXI

AMBA_AHB_Bus_Model.xml

Parameter Configuration

Hidden Parameters

Refresh: true or false. This parameter can turn on and off the refresh operation of the block.

Parameter |

Explanation |

Type |

Example |

Architecture_Name |

This is the name of the ArchitectureSetup block that this Memory is associated. If the ArchitectureSetup does not exist, a error will be generated and the model will be terminated. |

String |

"Architecture_1" |

Memory_Name |

This is an unique name of this Memory. No other Architecture, Script, SystemResource or Queue can have this name in a model. The memory name is used to identify this destination. |

String |

"SDRAM_1" |

Memory_Speed_Mhz |

Speed of the memory in Mhz. |

Double |

250.0 |

Memory_Size_MBytes |

Size of the Memory in MBytes. |

Double |

64.0 |

Access_Time |

This is the time taken to Access and return a requested value from the Memory cells. The value is in nano-seconds and is the time to access one memory_width in the memory array. The name (Read etc.) is matched with the A_Command field of the incoming Data Structure. The access time corresponding to this name is used. Default value is "Read 5.0,Prefetch 6.0,Write 7.0,ReadWrite 8.0, Erase 9.0”. The list can have any names and associated values. The entry here is flexible and the Memory_Speed can be used as an attribute of the calculation. |

String |

"Read 5.0, Prefetch 6.0, Write 7.0, ReadWrite 8.0, Erase 9.0"

"Read (5.0*1000.0/Memory_Speed_Mhz), Prefetch (6.0*1000.0/Memory_Speed_Mhz), Write (7.0*1000.0/Memory_Speed_Mhz), ReadWrite (8.0*1000.0/Memory_Speed_Mhz), Erase (9.0*1000.0/Memory_Speed_Mhz)" |

FIFO_Buffers |

This is an optional queue that can queue any requests. The default is 2. There is a single Queue for both the ports. This is a non-standard implementation and can be caused by the user, if required. |

Integer |

32 |

Refresh_Rate_Cycles |

The Refresh Rate of the DRAM. This is the number of cycles between refresh. The Refresh_Rate_Cycles/Memory_Speed_Mhz will be the time between refreshes. For a SRAM and when the refresh is not required, a hidden parameter called refresh can be added to the block and set to false. In that case, no refresh will be generated. |

Integer |

16384 |

Refresh_Cycles |

Refresh Cycles is the duration in cycles of the refresh. The Refresh_Cycles/Memory_Speed_Mhz will be the duration of the refresh. This translates to the number of cells that need to be refreshed. |

Integer |

32 |

Memory_Address |

This is a range of values and specifies the range of memory addresses that are associated with this Memory block. The format is "Min_Address,Max_Address". for example, "201,300". |

String |

"201,300" |

Controller_Time |

The Controller_Time provides the latency foe the memory controller. The value can be an expression that contains variables, fields of the incoming data structure, parameter, RegEx and any Expression line that is available in ExpressionList block. The value must be in "". The Controller_Time can be dynamic if references an incoming data structure field or a model variable. |

String |

"Cycle_Time * 1.0" |

Enable_Hello_Messages |

This will help other blocks

specifically buses for routing purpose. if it is true then a hello message will

be sent through output port with required information. |

Boolean |

true |

Width_Bytes |

Width of the memory in bytes and can be 1, 2, 4, 8, 16, 32, 64. |

- |

4 |

Memory_Type |

The different types of RAM supported. |

StringAttribute |

SDR |

Port |

Explanation |

input |

This port connects this block to a Bus_Port and is the default input port. This is the set of ports on the left side (West). |

output |

This port connects this block to a Bus_Port and is the default output port. This is the set of ports on the left side (West). |

input2 |

This port connects this block to a Bus_Port and is the second input port. This is the set of ports on the right side (East). |

output2 |

This port connects this block to a Bus_Port and is the second output port. This is the set of ports on the right side (East). |

Enabling Plots

To enalbe plots user can add Timing Diagram block

to the model (Hardware Setup -> TimingDiagram) and modify the

DRAM name in the configuration window. Green color plot shows the

transactions that are happening in the DRAM bllock.Statistics and Analysis

The following are the statistics that can be generated:1. Memory _Used_By_Source_MB:

The memroy utilized by each source devices in terms of Mega bytes are observed. Usage can be analyszed as Max, Mean, min and standard deviation.

2. Throughput_MBs:

The Throughput of the DRAM interms of Mega bytes. It can be analyzed as Max, mean, min and standard deviation.

3. Utilization_Pct:

The Utilization of the DRAM in the overall model as percentage during the simulation period.

4. Delay:

The delays that the DRAM block handled during the simulation period,

The following image shows the statistics that can be generated for the DRAM block using Architecture setup block.

Error messages and solution

1.Error : Block Overlaps with

(.AXI_Testing.Integrated_Cache.Script) with Name: L2_Cache_Block_Status

Exception : .AXI_Testing.RAM2 Name must be unique.

Please make sure the DRAM name is not used in any other block.

Line : Incoming Data Structure does not contain one

or more of the necessary fields:

{"A_Bytes_Remaining",

"A_Bytes_Sent"}

Error_Number : DRAM_001B

Explanation : Add the required fields listed.

Exception : Incoming Data Structure is missing some

fields

Please make sure the incoming data structure contains the necessary fields that are specified in the "Expected fields" section.

3.

Error : Token input to DRAM (DRAM2) is not Valid. Pl

recheck the Block connectivity

Exception : Token Found:

{A_Bytes = 32,

A_Bytes_Remaining = 8,

A_Bytes_Sent = 24,

A_Command = "Read",

A_Destination = "DRAM",

A_Hop

= "DRAM",

A_Instruction = {"ADD"},

A_Priority = 0,

A_Source = "Processor",

BLOCK

=

"Traffic3",

DELTA

= 0.0,

DS_NAME

=

"Header_Only",

ID

= 1,

INDEX

= 0,

TIME

= 0.0,

Time_Array = {0.0},

Trace_Array = {"DRAM2_in"}}

Please make sure there is no direct looping in the model with the DRAM block.

4.

Problem reading RecordToken Field:

A_Task_Flag

Exception Reported:

VisualSim.kernel.util.IllegalActionException: Problem reading RecordToken

Field: A_Task_Flag

Field does not exist.

Please make sure the incoming data structure contains the necessary fields that are specified in the "Expected fields" section.