Quick Explanation

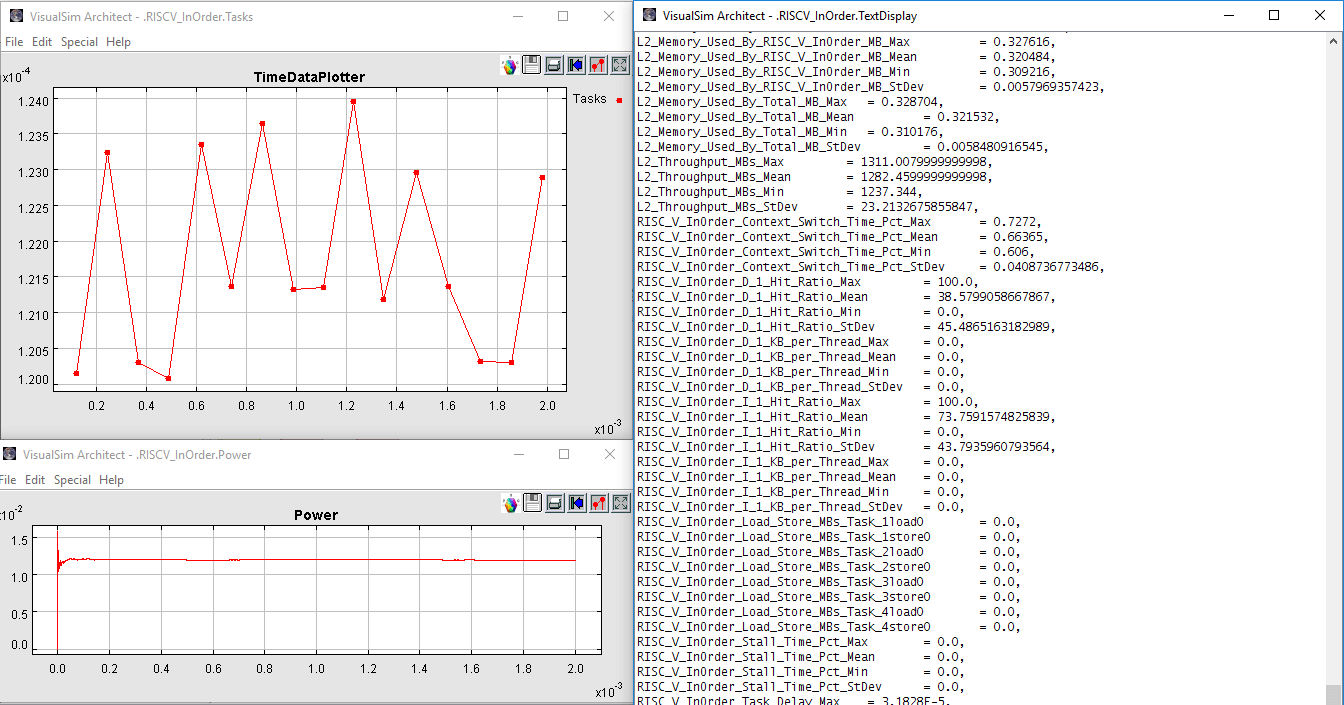

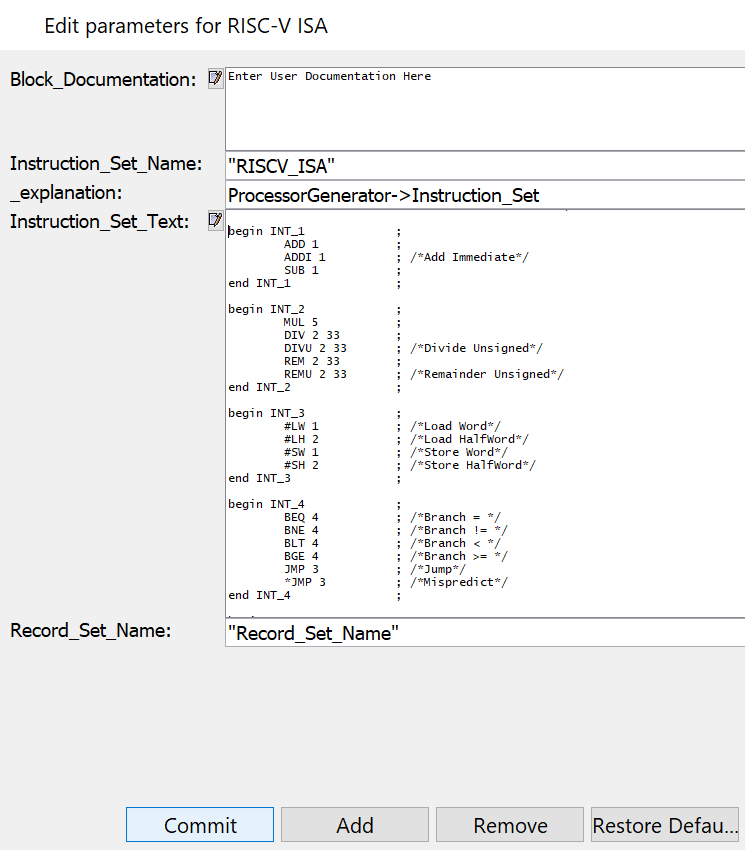

- Supports RV321 ISA

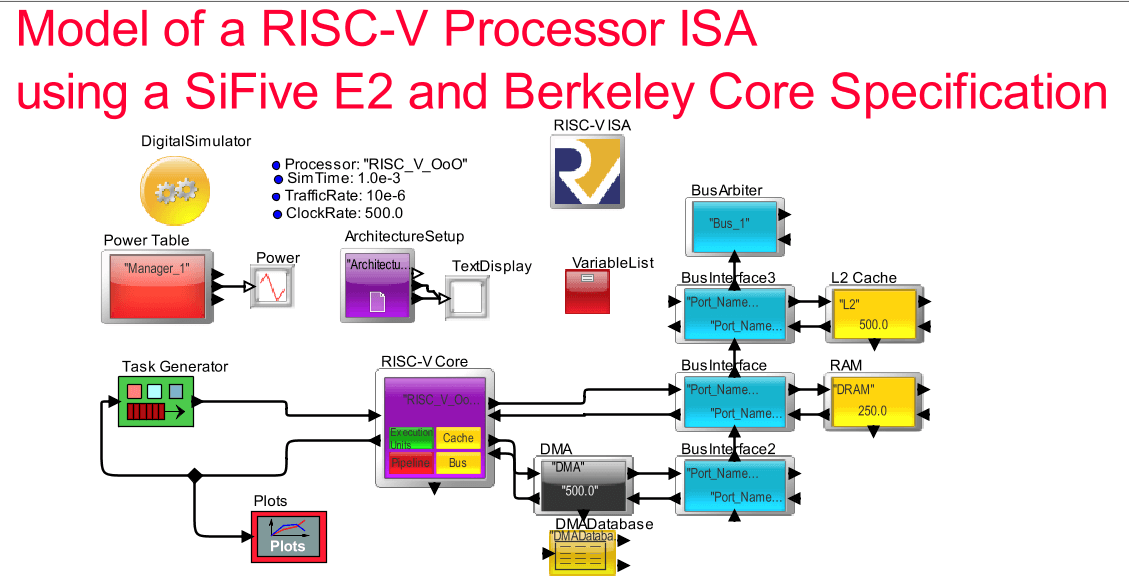

- Supports in-order and out-of-order pipeline

- Supports 5-stage pipeline

- Supports NpBench's networking task profile

Protocol

- Support processors from SiFive, Berkeley and other vendors

- Compare the application of RISC-V against ARM M4 and ARC

- Evaluate the benefit of using RISC-V in a new application